# DESCRIPTION

The FHX35X/002 Chip and FHX35LG/002 packaged devices are HEMT (High Electron Mobility Transistor) ones suitable for use as the front end of an optical receiver in high speed lightwave communication systems. This HEMT combines high transconductance, low gate capacitance and low leakage current; all important factors in achieving low noise preamplification. Fujitsu's stringent Quality Assurance criteria and detailed Test Procedures assure Highest Reliabilitity Performance.

# **FEATURES**

- High Transconductance

- Low Leakage Current

- Low Gate Capacitance

- Gold Bonding System

- Proven Reliability

| Item                    | Symbol           | Conditions      | Ratings    | Unit |  |  |  |  |  |

|-------------------------|------------------|-----------------|------------|------|--|--|--|--|--|

| Drain-Source Voltage    | VDS              |                 | 6          | V    |  |  |  |  |  |

| Gate-Source Voltage     | VGS              |                 | -5         | V    |  |  |  |  |  |

| Total Power Dissipation | Рт               |                 | 290        | mW   |  |  |  |  |  |

| Storage Temperature     | T <sub>stg</sub> |                 | -65 to 175 | °C   |  |  |  |  |  |

| Channel Temperature     | T <sub>ch</sub>  |                 | +175       | °C   |  |  |  |  |  |

| Thermal Resistance      | R <sub>th</sub>  | Channel to Case | 150        | °C/W |  |  |  |  |  |

#### ABSOLUTE MAXIMUM RATINGS (Ambient Temperature Ta=25°C)

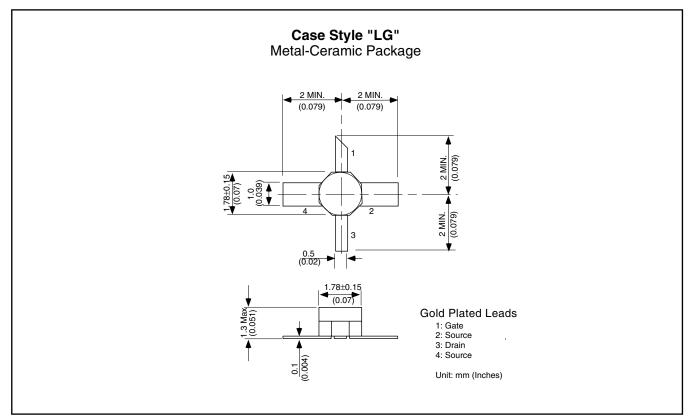

LG PACKAGE

#### ELECTRICAL CHARACTERISTICS (Ambient Temperature $T_a=25^{\circ}C$ )

| ltem                        | Symbol          | Conditions                                   |             | Limits |       |      | Unit |

|-----------------------------|-----------------|----------------------------------------------|-------------|--------|-------|------|------|

|                             | Symbol          |                                              |             | Min.   | Min.  | Max. | Unit |

| Drain Current               | IDSS            | $V_{DS}=2V, V_{GS}=0V$                       |             | 15     | 40    | 85   | mA   |

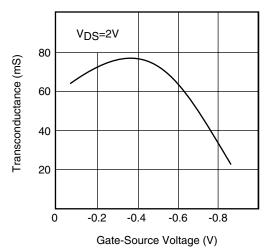

| Transconductance            | 9m              | V <sub>DS</sub> =2V, I <sub>DS</sub> =10mA   |             | 45     | 60    | -    | mS   |

| Pinch-off Voltage           | Vp              | V <sub>DS</sub> =2V, I <sub>DS</sub> =1mA    |             | -0.2   | -1.0  | -2.0 | V    |

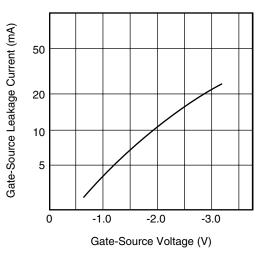

| Gate-Source Leakage Current | IGSO            | V <sub>GS</sub> =-2V                         |             | -      | 10    | 20   | nA   |

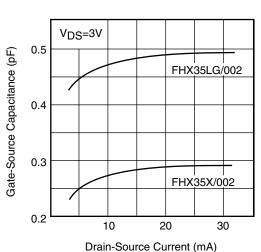

| Gate-Source Capacitance     | CGS             | V <sub>DS</sub> =3V<br>I <sub>DS</sub> =10mA | FHX35X/002  | -      | 0.27  | -    | рF   |

|                             |                 |                                              | FHX35LG/002 | -      | 0.47  | -    |      |

| Gate-Drain Capacitance      | C <sub>GD</sub> | V <sub>DS</sub> =3V, I <sub>DS</sub> =10mA   |             | -      | 0.035 | -    | pF   |

## Low Noise HEMT

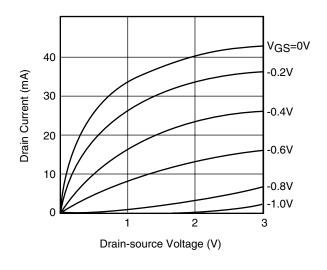

#### Fig. 1 Drain Current vs. Drain-Source Voltage

#### Fig. 3 Transconductance vs. Gate-Source Voltage

Fl

Fig. 4 Gate-Source Leakage Current vs. Gate-Source Voltage

# Fig. 2 Gate-Source Capacitance vs. Drain-Source Current

#### **BONDING PROCEDURE FOR FET CHIPs**

Caution must be excercised to prevent static build up by proper grounding of all equipment and personnel. All operations must be performed in a clean, dust-free and dry environment.

- 1. Storage Condition: Store in a clean, dry nitrogen environment.

- 2. Die-Attach

- 2.1 The die-attach station must have an accurate temperature control, and an inert forming gas should be used.

- 2.2 Chips should be kept at room temperature, except during die-attach.

- 2.3 Place package or carrier on the heated stage.

- 2.4 Place the solder at the position where the chip will be bonded.

- 2.5 Lightly grasp the chip edges using tweezers and scrub the die onto the Au-Sn solder preform. The die attach conditions are: 300 to 310° for 30 to 60 seconds. The Au-Sn (80-20) solder preform volume should be about 3.2x10<sup>-3</sup> mm<sup>3</sup> for FHX35X/002.

- 3. Wire Bonding

- 3.1 Bonding Condition

The bonder must be properly grounded. Wire bonding should be performed with a thermal compression bonder using 0.7 to 1.0 mil diameter, half hard, 3-8% elongation gold wire.

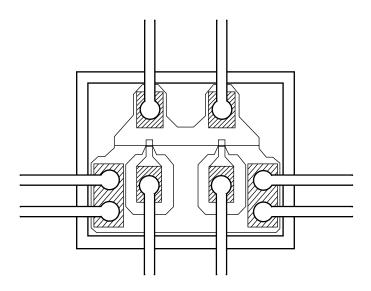

3.2 Wire Layout

The wire bonding should be performed as shown in the following example.

## Wire Layout

#### FHX35X/002

# Low Noise HEMT

#### For further information please contact:

#### FUJITSU COMPOUND SEMICONDUCTOR, INC.

2355 Zanker Rd. San Jose, CA 95131-1138, U.S.A. Phone: (408) 232-9500 FAX: (408) 428-9111 www.fcsi.fujitsu.com

#### FUJITSU MICROELECTRONICS EUROPE, GmbH Quantum Devices Division

Network House Norreys Drive Maidenhead, Berkshire SL6 4FJ Phone:+44 (0)1628 504800 FAX:+44 (0)1628 504888

#### CAUTION

Fujitsu Compound Semiconductor Products contain **gallium arsenide (GaAs)** which can be hazardous to the human body and the environment. For safety, observe the following procedures:

- Do not put these products into the mouth.

- Do not alter the form of this product into a gas, powder, or liquid through burning, crushing, or chemical processing as these by-products are dangerous to the human body if inhaled, ingested, or swallowed.

- Observe government laws and company regulations when discarding this product. This product must be discarded in accordance with methods specified by applicable hazardous waste procedures.

Fujitsu Limited reserves the right to change products and specifications without notice. The information does not convey any license under rights of Fujitsu Limited or others.

© 1998 FUJITSU COMPOUND SEMICONDUCTOR, INC. Printed in U.S.A. FCSI0598M200